2、層的定義:BEGIN Layer(Top)層:REGULAR-PAD < THERMAL-PAD = ANTI-PAD

END LAYER(同BEGIN,常用copy begin layer, then paste it)

TOP SOLDERMASK:只定義REGULAR-PAD ,大于(Begin layer層regular-pad,約為1.1~1.2倍)

BOTTOM SOLDERMASK(同Top soldermask,常用Top soldermask, then paste it) * Y% [' n# c' n; _8 A, k3 |0 b f* n

例1 //---------------------------------------------------------------------------------------

Padstack Name: PAD62SQ32D + ^' y: r" L+ c: B5 w% O

1 ]- o# G* Z( C ]& \

*Type: Through ) t+ e r; C' G A* Q! D

*Internal pads: Fixed + c$ }$ `: s" d$ z$ A7 j

*Units: MILS

Decimal places: 4

0 O8 A' u4 e$ i Y$ |4 l& n

Layer Name Geometry Width Height Offset (X/Y) Flash Name Shape Name 8 P1 Z4 g% s4 Y# E. x9 l2 K9 g% S

------------------------------------------------------------------------------------------------------------------ / P3 J6 S9 R6 _) `

*BEGIN LAYER

*REGULAR-PAD Square 62.0000 62.0000 0.0000/0.0000 % D# j" o0 K3 z& Z) d

*THERMAL-PAD Circle 90.0000 90.0000 0.0000/0.0000

*ANTI-PAD Circle 90.0000 90.0000 0.0000/0.0000

*END LAYER(同BEGIN,常用copy paste) * [) o" _2 j8 G( X

DEFAULT INTERNAL(Not Defined )

*TOP SOLDERMASK

*REGULAR-PAD Square *75.0000 75.0000 0.0000/0.0000 ) @7 S& `- k" ~) a2 k3 f. ]8 j

*BOTTOM SOLDER MASK ) p4 l# }0 M) d8 w" |& u

*REGULAR-PAD Square *75.0000 75.0000 0.0000/0.0000

TOP PASTEMASK(Not Defined )

BOTTOM PASTEMASK(Not Defined ) . G) F6 E% D: ?# e6 ]9 T! Q

TOP FILMMASK(Not Defined ) 1 ]; Y( P/ X" c7 y4 `( N6 d, i4 H

BOTTOM FILMMASK(Not Defined ) 9 p5 ?) o% O9 Z/ L, u9 U

NCDRILL * P" Y4 n/ p3 m) d

32.0000 Circle-Drill Plated Tolerance: +0.0000/-0.0000 Offset: 0.0000/0.0000

DRILL SYMBOL * A3 T9 f& m; l! v2 o

Square 10.0000 10.0000 - l5 R% |/ A! W; E4 I5 S, L

----------------------------------------------

表貼焊盤的設計: 3 R7 Y! }9 E( b" _

1、定義,類型single,中間層(option),鉆孔(圓形,內(nèi)壁鍍錫plated,尺寸一定為0) ; Q6 ]6 Q Q8 R

2、層的定義:BEGIN Layer(Top)層:只定義REGULAR-PAD

TOP SOLDERMASK:只定義REGULAR-PAD ,大于(Begin layer層regular-pad,約為1.1~1.2倍)

例2 ------------------------------------------------ $ R5 i# V- u& C1 a

Padstack Name: SMD86REC330

*Type: Single

*Internal pads: Optional

*Units: MILS

Decimal places: 0 9 z$ q% W; {- \9 s: j, |1 u

Layer Name Geometry Width Height Offset (X/Y) Flash Name Shape Name

------------------------------------------------------------------------------------------------------------------

*BEGIN LAYER

*REGULAR-PAD Rectangle 86 330 0/0

THERMAL-PAD Not Defined

ANTI-PAD Not Defined

END LAYER(Not Defined ) 1 r( `! |6 g$ _ i4 l& A2 E q/ W

DEFAULT INTERNAL(Not Defined )

*TOP SOLDERMASK

*REGULAR-PAD Rectangle 100 360 0/0 5 ^4 P! j! p" o* B4 g- z

BOTTOM SOLDERMASK(Not Defined )

TOP PASTEMASK(Not Defined ) / A F4 o% u, Y4 y/ q2 ^

BOTTOM PASTEMASK(Not Defined )

TOP FILMMASK(Not Defined )

BOTTOM FILMMASK(Not Defined ) $ l9 \& {; D' @) o

NCDRILL(Not Defined ) " c6 V9 [; G" d; H9 Y

DRILL SYMBOL # l0 b) V {6 S& \- d" D) ~7 b

Not Defined 0 0

------------------------------------------

9 X) O8 i. e" o% P* O6 @ K x

手工建立元件(主要包含四項:PIN;Geometry:SilkScreen/Assembly;Areas:Boundary/Height;RefDes:SilkScreen/Display) - ~" i3 c+ a& l1 f' I' P7 w

注意:元件應放置在坐標中心位置,即(0,0)

1、File ew..package symbol ) `1 g1 g! L9 p& {% g

2、設定繪圖區(qū)域:SetupDrawing size...Drawing parameter... & b9 D) b N2 H8 i* i% p

3、添加pin:選擇padstack ,放置,右排時改變text offset(缺省為-100,改為100)置右邊 8 g% D, c6 @. J# ^5 y

4、添加元件外形:(Geometery)

*絲印層Silkscreen:AddLine(OptionActive:package geometery;subclass:silkscreen_top) " x( _* W8 ]0 ?! O+ C

*裝配外框Assembly:AddLine(OptionActive:package geometery;subclass:Assembly_top)

5、添加元件范圍和高度:(Areas)

*元件范圍Boundary:SetupAreaspackage boundary....Add Line(OptionActive Class

ackage geometry;subclass

ackage geometry;subclass ackage_bound_top) ) d, \2 r9 M1 ]! n2 h

ackage_bound_top) ) d, \2 r9 M1 ]! n2 h]]>

. Cadence allegro. aMS Simulator

. Cadence PSpice. simulation Cadence PSpice仿真

該產(chǎn)品與allegro design entry HdL和Cadence OrCad. Capture緊密集成,同時該仿真技術也可以在強大的協(xié)同仿真環(huán)境,SLPS,中與MathWorks的MaTLaB Simulink軟件包連接,見圖1。

優(yōu)點

. 改善大型設計的仿真次數(shù),可靠性和收斂

. 通過整合的模擬和事件驅(qū)動的數(shù)字仿真既提高了速度,又無需犧牲準確性

. 利用基本直流,交流,噪聲和瞬態(tài)分析來探測電路行為

. 允許使用SLPS進行實際電氣設計的系統(tǒng)級接口的測試

. 超過20,000個模擬和混合信號模型庫供選擇

. 允許模擬和數(shù)字信號的自動識別,并應用到模擬到數(shù)字和數(shù)字到模擬接口

. 在付諸硬件實施之前使用假設的理念來CADENCE

PCB設計仿真

混合模擬/數(shù)字仿真

集成的模擬和事件驅(qū)動數(shù)字仿真提高了速度而無需犧牲精確性,單獨的圖形化波形分析器在同一時間軸上顯示混合模擬和數(shù)字仿真的結(jié)果,數(shù)字功能支持5種邏輯電平和64種強度,由負載而定的延遲,以及hazard/race檢查, allegro aMS Simulator 和PSpice仿真還具有針對數(shù)字門和約束檢查,如setup和hold時序的傳播建模特性,

模擬分析

使用直流,交流,噪聲,瞬態(tài),參數(shù)掃描,蒙特卡洛和直流敏感性分析探測電路行為,allegro aMS Simulator和PSpice技術包含若干交互仿真控制器和兩個仿真解算器。

圖形結(jié)果和數(shù)據(jù)顯示

Probe Windows允許用戶從擴展的一組數(shù)學函數(shù)中進行選擇,用于仿真輸出變量, 通過在原理圖內(nèi)直接將標記放置在所希望的管腳,網(wǎng)絡,和零件上,設計師可以創(chuàng)建繪圖窗口模板并用它們?nèi)菀椎剡M行復雜的量測, 使用內(nèi)置的量測函數(shù)和定制量測的創(chuàng)建, 該工具還可以幫用戶測量電路的性能特征,為顯示數(shù)據(jù),附加的功能允許進行電路電壓,電流和功耗的實際和復雜函數(shù)繪圖,包括用于幅值和相位裕度的Bodé圖及用于小信號特征的導數(shù),見圖2。

尋求設計的關系

. 使用優(yōu)化器優(yōu)化電路性能

. 使用數(shù)學表達式,函數(shù)和行為器件替代和仿真復雜電路的功能模塊,

. 使用應力分析并通過使用蒙特卡洛分析觀察組件成品率,確定哪個組件受載過大,

特性

Cadence的PCB設計仿真技術與Cadence的從前端到后端PCB設計流程無縫集成,使用于仿真和PCB設計的單獨,統(tǒng)一的設計環(huán)境的實現(xiàn)成為可能。

設計輸入和編輯

使用Cadence原理圖設計輸入技術,可從超過18,000個符號和模型的庫中選擇以進行設計仿真,它提供許多特性,使得原理圖輸入和模擬仿真設計變得容易,這兩項集成都包括一鍵仿真和交叉探測和許多其他的仿真工具。

激勵創(chuàng)建

使用可參數(shù)化描述的內(nèi)置函數(shù)或用鼠標手繪分段線性,PWL,信號來創(chuàng)建任意形狀的激勵,為信號,時鐘和總線創(chuàng)建數(shù)字激勵,單擊并拖動以引入和移動轉(zhuǎn)換。

電路仿真

用戶可以很容易地建立和運行仿真,然后從Probe交叉探測仿真結(jié)果,Probe是一個業(yè)界標準的波形觀察器,對多種仿真profile的支持使用戶可以在同一原理圖上調(diào)用并運行不同的仿真,仿真偏置結(jié)果可以在原理圖上直接進行觀察,包括節(jié)點電壓,器件功率計算,管腳和支路電流,對檢查點重啟的支持,允許設計師在同一電路以很少的改變進行多次仿真時,減少仿真的次數(shù)。

MOdeLS模型

內(nèi)含大量不同的精確內(nèi)部模型,它通常有溫度效應,為仿真添加了靈活性,模型有R,L,C和二極管,以及,

. 內(nèi)置IGBT

. 七種MOSFeT模型,包括業(yè)界標準的BSIM3v3.2和新的eKV 2.6模型

. 五種GaasFeT模型,包括Parker-Skellern 和 TriQuint TOM-2,TOM-3模型

. 非線性 磁性模型,具備飽和與磁滯現(xiàn)象

. 整合了延遲,反射,損失,散射和串擾的傳輸線性模型. 數(shù)字原件,包括帶有模擬I/O模型的雙向

傳輸門

. 兩種電池模型,允許對放電周期和運行條件進行精確仿真器件方程開發(fā)包,dedK,允許新的內(nèi)部模型方程的實現(xiàn),這些方程可以同allegro aMS Simulator和PSpice仿真一起使用。

模型庫

用戶可以從北美,日本,歐洲生產(chǎn)的超過18,000種模擬和混合信號器件模型, 及超過4,500種BJT,JFeT,MOSFeT, IGBT,SCR,磁芯和螺線管,功率二極管和橋接器,運算放大器,光電耦合器,調(diào)節(jié)器, PWM控制器,乘法器,定時器和采樣保持器等參數(shù)化的模型中進行選擇。

模型編輯

可以很容易地抽取所支持器件類型的模型,只需輸入器件技術資料中要求的數(shù)據(jù)。

行為建模

功能模塊使用數(shù)學表達式和函數(shù)進行描述,允許設計師充分利用一整套數(shù)學運算器,非線性函數(shù)和濾波器,電路行為可以在時域或頻域使用公式,包括拉普拉斯變換,或查找表進行定義,錯誤和警告信息可以在不同條件下進行指定,用戶可以容易地選擇在一個層級中已被傳遞到子電路的參數(shù),并將它們插入傳遞函數(shù)中,新的行為功能包括in(x), exp(x),sqrt(x)等數(shù)學函數(shù)。

磁性零件編輯

磁性零件編輯器可以幫助設計師解決手工設計變壓器時遇到的問題,用戶可以設計磁性變壓器和直流電感,并為可用于allegro aMS仿真器電路的變壓器和電感生成仿真模型,磁性零件編輯器還允許設計師生成制造變壓器或感應器所需的數(shù)據(jù), 設計過程完成后由Magdesigner生成的制造商報告,包含了廠商生產(chǎn)商用變壓器所需的全部數(shù)據(jù)。

]]>|

最近實驗室項目很忙,很久沒有來更新博客了,由于項目需要,這段時間一直在做FPGA,自己還學習了用Cadence畫電路板,做了一塊FPGA開發(fā)板,前幾天調(diào)試通過了,這幾天還得繼續(xù)編寫控制程序(包括AD(型號AD9238)高速緩存控制程序,串口讀寫程序,DDS(型號AD9958)頻率掃描配置程序,電子開關控制程序等),時間很緊,挑戰(zhàn)還是比較大啊,呵呵,下面寫點學習Cadence和FPGA的總結(jié): Cadence 學習: 關于Cadence的書籍不是很多,我看了以下幾本: 1、《Cadence高速電路板設計與仿真》:書很厚,內(nèi)容最全,但感覺很多直接翻譯Cadence的help文件,只講怎么操作,沒有講清楚為什么這么操作,我主要在里面學習了orCAD(CIS,orCAD 是后來被Cadence收購的,現(xiàn)在已經(jīng)被Cadence整合進去,和其他軟件實現(xiàn)無縫連接)的基本操作。 2、《Cadence Concept HDL&&Allegro 原理圖和PCB設計》:EDA先鋒工作室出的書我一直認為是比較不錯的,這本也不例外,但是Cadence Concept HDL(HDL)這個原理圖設計工具感覺沒有orCAD(CIS)操作來的方便,所以我主要從這本書上學習了Allegro的操作,本書對Allegro的講解感覺比上一本書好理解。 3、《Cadence高速PCB設計與仿真分析》:Cadence功能強大,純粹的畫電路板功能只是其很小一部分功能,其還可以在高速電路設計,信號完整性(SI),電源完整性(PI)仿真等方面發(fā)揮強大的功能,這本書上涉及到一部分高速PCB仿真的內(nèi)容,書的后面幾章講解model integrity(查看,編輯IBIS模型),PCB SI,SigXploer等工具。 4、除了以上幾本書外,網(wǎng)上一直流傳著中興公司內(nèi)部的Cadence培訓教程,共5個分冊:原理圖分冊,PCB設計分冊,約束管理器分冊,自動布線器分冊,仿真分冊,里面的講解也很詳細,很多內(nèi)容都是直接從實際出發(fā)開始講解,需要的人可以給我留言,我會發(fā)給大家。 5、在Cadence的學習中感覺這幾個論壇不錯: http://www.eda365.com/index.php http://www.eda365.com/index.php 6、在Cadence的學習中我認為主要要把握一下幾點: a、焊盤文件的建立(.pad),分清楚各種焊盤的區(qū)別,在各層中的結(jié)構,剛從protel直接轉(zhuǎn)型用Cadence,這一點一定要注意。下面給一張比較詳細的示意圖,便于大家理解  b、分清楚電路板上各個層的含義,一般兩層板都會有頂層(底層)絲印層(silk),頂層(底層)阻焊層(soldermask)(阻焊層即為在電路板上不刷那層綠油的層),頂層(底層)布線層(etch),其它層根據(jù)具體要求再設置。 c、Cadence的操作都是先選操作內(nèi)容,再選操作對象,這一點剛開始很不習慣,用多了以后感覺這是它的一個優(yōu)點。 d、遺憾的一點是Cadence輸出的鉆孔文件不支持橢孔(olong),主要自己畫多個圓過孔來模擬,不知道有沒有其他方法。 下面講講FPGA的學習: 講FPGA的學習之前不得不提硬件描述語言(HDL),我主要用的是Verilog語言,另外一種常用的就是VHDL語言,兩種語言各有優(yōu)劣,對于Verilog的學習我主要推薦以下兩本書: 1、《verilog 數(shù)字系統(tǒng)設計教程》,這本書對于入門是一本很好的書,通俗易懂,讓人很快上手,它里面的例子也不錯。但本書對于資源優(yōu)化方面的編程沒有多少涉及到。 2、《設計與驗證Verilog HDL》,這本書雖然比較薄,但是相當精辟,講解的也很深入,很多概念看了這本書有種豁然開朗的感覺,呵呵。 其實Verilog語言是相當容易上手的,主要是要建立一個硬件電路編程的概念,很多模塊都是并行的,而不是軟件編程中的串行。要先畫電路模塊方框圖再進行程序的編寫。 下面講講FPGA的學習,其實剛開始由于程序規(guī)模不是很大,我用的是CPLD(MAXII系列的),后來規(guī)模大了,尤其是AD高速緩存中要用到FIFO,CPLD中沒有RAM,所以自己又做了FPGA(cycloneII系列)的板子。其實MAXII系列和FPGA的內(nèi)部結(jié)構已經(jīng)很像了,都是基于LUT的。CPLD 和FPGA的界限也越來越模糊。FPGA學習中也主要看了兩本EDA先鋒工作室出的書: 1、《Altera FPGA/CPLD 設計(基礎篇)》:講解一些基本的FPGA設計技術,以及QuartusII中各個工具的用法(IP,RTL,SignalProbe,SignalTapII,Timing Closure Floorplan,chip Editor等),對于入門非常好。 2、《Altera FPGA/CPLD 設計(高級篇)》:講解了一些高級工具的應用,LogicLock,時序約束很分析,設計優(yōu)化,也講述了一些硬件編程的思想,作為提高用。 3、《FPGA設計指南--器件,工具和流程》:這本書看了他的目錄忍不住就買了,這本書講述了FPGA設計的各個方面,雖然每個方面都是點到為止,但能讓你有個整體的概念,了解FPGA的所有設計功能,了解FPGA開發(fā)的整個流程。 4、FPGA的學習其實不難,剛開始看到他有這么多引腳,很多人就害怕,其實大部分引腳都是IO口,由你隨意定義,真正的控制及配置管腳很少,一般書上都會說明這些腳怎么連接,自己對照著畫個FPGA的板子,再在上面調(diào)試一些例程,這樣學起來還是很快的。下面曬一下我自己畫的FPGA開發(fā)板,F(xiàn)PGA是ep2c5,配置芯片是EPCS1,其實也不能叫做開發(fā)板,由于項目要求面積小,只接了幾個開關和LED,其他引腳全部用插針連出來了,比較失敗的是四個定位孔畫的太大了,呵呵

|

目前,Cadence設計系統(tǒng)公司新推出Cadence Allegro系統(tǒng)互聯(lián)設計平臺,據(jù)稱此平臺具有縮短PCB設計周期,提高生產(chǎn)效率的特點。

Cadence宣稱,Allegro平臺15.2版有利于約束驅(qū)動式PCB設計,并促使多種類型新產(chǎn)品的問市以迎接集成芯片(IC)封裝和千兆赫茲信號的設計挑戰(zhàn)。該平臺引進了協(xié)同設計和數(shù)據(jù)庫數(shù)據(jù)管理方案。

泰克公司工程工具部主任Bart Welling 表示,“泰克選擇了最新版的Cadence Allegro平臺作為我們初步的模擬/混合-模式ASIC、封裝以及PCB開發(fā)工具包。Allegro平臺具有縮短原型生產(chǎn)周期的新功能,因此,約束驅(qū)動式設計流程早在設計師的工作臺上就已經(jīng)開始了。”

據(jù)介紹,通過Allegro平臺產(chǎn)品進行新約束設計,能夠記錄在IC封裝和通道中固有的關鍵信號延時,并能幫助設計師花費最短的時間連接封裝數(shù)據(jù)庫或手動記錄這些關鍵信號的延時,從而使工程師能夠在設計過程中更加靈活地提高設計的精確度。

Allegro Design Entry HDL是自新款Allegro平臺推出之后的主要產(chǎn)品,它負責在設計輸入整個過程中對相同擴展網(wǎng)絡的生成和仿真提供前端的支持。通過改進頁面管理操作以及應用改進的跨信號網(wǎng)約束設計,它提高了工作效率。

工程團隊在設計和管理當今復雜的電子設計全系統(tǒng)互連時,面臨前所未有的挑戰(zhàn)。隨著PCB平均面積的減小,器件管腳數(shù)、設計頻率和設計約束復雜度卻不斷提升。這種持續(xù)的挑戰(zhàn)使

得傳統(tǒng)PCB設計方法變得越來越力不從心。基于Cadence在PCB領域的領先地位,新的Allegro平臺提供了能夠適應和解決這些不斷增加的復雜度難題的流程和方法學,從而樹立了全新PCB設計典范。

“新的Allegro平臺版本引入了很多新的生產(chǎn)率特性,將為象我一樣的設計師帶來優(yōu)勢,”加拿大Kaleidescape高級PCB設計師 Vincent Di Lello說:“象物理和空間約束特性,名詞-動詞選擇模式,擴展的RMB功能,開放的GL和無數(shù)可視的增強功能將大大增加設計師的輸出,并提供一個更加界面友好的設計環(huán)境。”

Cadence Allegro平臺是基于物理和電氣約束驅(qū)動的領先PCB版圖和互連系統(tǒng)。它經(jīng)過升級,現(xiàn)在已包含了針對物理和空間約束的最先進的布線技術和全新方法學。它使用了Cadence 約束管理系統(tǒng),那是在整個PCB流程中提供約束管理的通用控制臺。其他升級包括支持先進串行連接設計的算法建模、改進的電路仿真、同Cadence OrCAD? 產(chǎn)品的無縫擴展性、增強的協(xié)同性、及新的用戶界面,從而可以提高生產(chǎn)力和可用性。該版本Allegro平臺還為信號完整性(SI)和電源完整性(PI)提供了重大的新功能。

“這是近年來最重要的PCB發(fā)布,我們一直在協(xié)助客戶滿足他們的需求,以便他們解決最具挑戰(zhàn)性的設計問題,”Cadence負責產(chǎn)品營銷的全球副總裁Charlie Giorgetti表示,“我們?yōu)榭蛻糸_發(fā)并提供創(chuàng)新的能力,顯見我們對PCB市場的承諾。”

最新發(fā)布的Cadence Allegro平臺,推出了層次布線規(guī)劃,和全局布線等新技術,大大提升了基于規(guī)則驅(qū)動的先進設計能力。該平臺還通過新的使用模式和增強的易用性提供了更好的可用性。所有版本的Allegro PCB設計平臺均包含新的PCB編輯技術,通過降低新方案學習曲線和優(yōu)化工具交互,可以提升設計師的效率和生產(chǎn)力。

改進的設計生成和仿真

Allegro平臺的這一版本利用最新版的Allegro System Architect,使硬件設計師可以縮短開發(fā)時間,生成比原來多60%的更大數(shù)量的差分信號。Cadence 通過向Cadence PSpice?技術增加重大的性能和收斂改進,進一步增強了模擬仿真。

先進的約束驅(qū)動設計

Allegro約束管理系統(tǒng)提供了一項先進的新性能,可減少含先進I/O接口設計的生成時間,這些接口有PCI Express、DDR2、SATA等。該系統(tǒng)使設計師有能力生成和指定利用參考其他對象規(guī)則的約束。約束管理系統(tǒng)包含了部件手冊,除物理和空間約束外,還為設計約束、設計規(guī)則檢查及屬性提供了位置。

提升的生產(chǎn)率和仿真精確性

新發(fā)布的Allegro平臺在Allegro PCB SI 及PCB PI中提供了新的功能,可縮短互連設計時間并提升產(chǎn)品性能和可靠性。這些性能包括了串行連接設計的顯著改進,從而允許用戶精確預測6 Gbps以上高級算法收發(fā)器通道的誤碼率概況。另外,通道兼容性和統(tǒng)計分析性能還允許用戶評估傳統(tǒng)通道,以便同高數(shù)據(jù)率收發(fā)器共用。

Allegro PCB PI選項可吸收來自IC及IC封裝設計工具的封裝寄生現(xiàn)象、裸片電容和轉(zhuǎn)換電流,以精確建立完整的電源供應系統(tǒng)。結(jié)合靜態(tài)IR降分析,Allegro PCB PI用戶可以快速判斷電源分配系統(tǒng)是否能維持規(guī)范所述參考電壓。

發(fā)布情況

Allegro PCB設計L、XL及GXL平臺版本計劃于2007年6月發(fā)布。PCB West上演示的全局布線環(huán)境(Global Route Environment)包含在Allegro PCB Design GXL產(chǎn)品中。

]]>◆按value值(For Allegro).

◆按Device 值(For Allegro)

1.編輯元件的封裝形式

在Allegro元件庫中value形式為“!0_1uf__bot_!”,在ORCAD元件屬性中已有相應value項“0.1uf (bot)”。 可以使用以下方法編輯元件 value值:

1)編輯單個元件

2)編輯單頁電路圖中所有元件

3)編輯所有元件

2、修改Create Netlist中的參數(shù)

在Other欄中的Formatters中選擇telesis.dll.將PCB Footprint中的{PCB Footprint}改為{value}。保存路徑中的文件后綴名使用.txt,如下圖所示

1.編輯元件的封裝形式

在Allegro元件庫中Device Name形式為“! smd_cap_0603!”,在RCAD元件屬性的Device項中并沒有相應項。因此須新建該項。建立的過程可以使用下面的方法:

1)直接雙擊元件編輯元件的屬性

Allegro平臺15.2版的推出使約束驅(qū)動式PCB設計又上了一個新的臺階并且促使多種類型新產(chǎn)品的問市以迎接不斷增多的集成芯片(IC)封裝和千兆赫茲信號的設計挑戰(zhàn)。該平臺引進了創(chuàng)新的協(xié)同設計和數(shù)據(jù)庫數(shù)據(jù)管理方案。

通過Allegro 平臺產(chǎn)品進行新約束設計,能夠記錄在IC封裝和通道中固有的關鍵信號延時,并能幫助設計師花費最短的時間連接封裝數(shù)據(jù)庫或手動記錄這些關鍵信號的延時,從而使工程師能夠在設計過程中更加靈活地提高設計的精確度。

Allegro Design Entry HDL是自新款Allegro平臺推出之后的主要產(chǎn)品,它負責在設計輸入整個過程中對相同擴展網(wǎng)絡的生成和仿真提供前端的支持。通過改進頁面管理操作以及應用改進的跨信號網(wǎng)約束設計, 本新產(chǎn)品大大地提高了工作效率。

Allegro新版平臺的的推出還為它的Allegro PCB Editor、Allegro PCB SI和Allegro Constraint Manager增添了新的特性和技術。Allegro PCB Editor增加了UNDO/REDO功能及互動布線調(diào)節(jié)功能,能夠提供實時反饋信息;Allegro PCB SI在性能上做了許多改進,以更加便于使用,支持IBIS 4.0,與3D場提取器整合后可用于封裝設計以及具有縮短布局后驗證時間的新功能;在Allegro Constraint Manager使用了新的屬性工作清單,改進了使用性能之后,工作效率有了顯著的提高。

]]>“隨著供電電壓下降和電流需要增加,在設計PCB">PCB系統(tǒng)上的功率提交網(wǎng)絡(Power Delivery Network)過程中必須考慮封裝和IC特性,”華為公司SI經(jīng)理姜向中說。“利用Allegro PCB">PCB PI技術的增強性能,我們能夠植入封裝模型,片上電流面圖和裸片電容,在提高精度的同時無需犧牲仿真性能。”

工程團隊在設計和管理當今復雜的電子設計全系統(tǒng)互連時,面臨前所未有的挑戰(zhàn)。隨著PCB">PCB平均面積的減小,器件管腳數(shù)、設計頻率和設計約束復雜度卻不斷提升。這種持續(xù)的挑戰(zhàn)使得傳統(tǒng)PCB">PCB設計方法變得越來越力不從心。基于Cadence在PCB">PCB領域的領先地位,新的Allegro平臺提供了能夠適應和解決這些不斷增加的復雜度難題的流程和方法學,從而樹立了全新PCB">PCB設計典范。

“新的Allegro平臺版本引入了很多新的生產(chǎn)率特性,將為象我一樣的設計師帶來優(yōu)勢,”加拿大Kaleidescape高級PCB">PCB設計師 Vincent Di Lello說:“象物理和空間約束特性,名詞-動詞選擇模式,擴展的RMB功能,開放的GL和無數(shù)可視的增強功能將大大增加設計師的輸出,并提供一個更加界面友好的設計環(huán)境。”

Cadence Allegro平臺是基于物理和電氣約束驅(qū)動的領先PCB">PCB版圖和互連系統(tǒng)。它經(jīng)過升級,現(xiàn)在已包含了針對物理和空間約束的最先進的布線技術和全新方法學。它使用了Cadence 約束管理系統(tǒng),那是在整個PCB">PCB流程中提供約束管理的通用控制臺。其他升級包括支持先進串行連接設計的算法建模、改進的電路仿真、同Cadence OrCAD? 產(chǎn)品的無縫擴展性、增強的協(xié)同性、及新的用戶界面,從而可以提高生產(chǎn)力和可用性。該版本Allegro平臺還為信號完整性(SI)和電源完整性(PI)提供了重大的新功能。

“這是近年來最重要的PCB">PCB發(fā)布,我們一直在協(xié)助客戶滿足他們的需求,以便他們解決最具挑戰(zhàn)性的設計問題,”Cadence負責產(chǎn)品營銷的全球副總裁Charlie Giorgetti表示,“我們?yōu)榭蛻糸_發(fā)并提供創(chuàng)新的能力,顯見我們對PCB">PCB市場的承諾。”

下一代PCB">PCB設計流程

最新發(fā)布的Cadence Allegro平臺,推出了層次布線規(guī)劃,和全局布線等新技術,大大提升了基于規(guī)則驅(qū)動的先進設計能力。該平臺還通過新的使用模式和增強的易用性提供了更好的可用性。所有版本的Allegro PCB">PCB設計平臺均包含新的PCB">PCB編輯技術,通過降低新方案學習曲線和優(yōu)化工具交互,可以提升設計師的效率和生產(chǎn)力。

改進的設計生成和仿真

Allegro平臺的這一版本利用最新版的Allegro System Architect,使硬件設計師可以縮短開發(fā)時間,生成比原來多60%的更大數(shù)量的差分信號。Cadence 通過向Cadence PSpice?技術增加重大的性能和收斂改進,進一步增強了模擬仿真。

先進的約束驅(qū)動設計

Allegro約束管理系統(tǒng)提供了一項先進的新性能,可減少含先進I/O接口設計的生成時間,這些接口有PCI Express、DDR2、SATA等。該系統(tǒng)使設計師有能力生成和指定利用參考其他對象規(guī)則的約束。約束管理系統(tǒng)包含了部件手冊,除物理和空間約束外,還為設計約束、設計規(guī)則檢查及屬性提供了位置。

提升的生產(chǎn)率和仿真精確性

新發(fā)布的Allegro平臺在Allegro PCB">PCB SI 及PCB">PCB PI中提供了新的功能,可縮短互連設計時間并提升產(chǎn)品性能和可靠性。這些性能包括了串行連接設計的顯著改進,從而允許用戶精確預測6 Gbps以上高級算法收發(fā)器通道的誤碼率概況。另外,通道兼容性和統(tǒng)計分析性能還允許用戶評估傳統(tǒng)通道,以便同高數(shù)據(jù)率收發(fā)器共用。

Allegro PCB">PCB PI選項可吸收來自IC及IC封裝設計工具的封裝寄生現(xiàn)象、裸片電容和轉(zhuǎn)換電流,以精確建立完整的電源供應系統(tǒng)。結(jié)合靜態(tài)IR降分析,Allegro PCB">PCB PI用戶可以快速判斷電源分配系統(tǒng)是否能維持規(guī)范所述參考電壓。

發(fā)布情況

Allegro PCB">PCB設計L、XL及GXL平臺版本計劃于2007年6月發(fā)布。PCB">PCB West上演示的全局布線環(huán)境(Global Route Environment)包含在Allegro PCB">PCB Design GXL產(chǎn)品中。 ]]>

Allegro 擁有完善的 Constraint 設定,用戶只須按要求設定好布線規(guī)則,在布線時不違反 DRC 就可以達到布線的設計要求,從而節(jié)約了煩瑣的人工檢查時間,提高了工作效率!更能夠定義最小線寬或線長等參數(shù)以符合當今高速電路板布線的種種需求。

軟件中的 Constraint Manger(圖 1 ) 提供了簡潔明了的接口方便使用者設定和查看 Constraint 宣告。它與Cadence? OrCAD? Capture 的結(jié)合讓 E.E. 電子工程師在繪制線路圖時就能設定好規(guī)則數(shù)據(jù),并能一起帶到Allegro工作環(huán)境中,自動在擺零件及布線時依照規(guī)則處理及檢查,而這些規(guī)則數(shù)據(jù)的經(jīng)驗值均可重復使用在相同性質(zhì)的電路板設計上。

Allegro 除了上述的功能外,其強大的自動推擠 push 和貼線 hug 走線以及完善的自動修線功能更是給用戶提供極大的方便;強大的貼圖功能,可以提供多用戶同時處理一塊復雜板子,從而大大地提高了工作效率。或是利用選購的切圖功能將電路版切分成各個區(qū)塊,讓每個區(qū)塊各有專職的人同時進行設計 ,達到同份圖多人同時設計并能縮短時程的目的 。用戶在布線時做過更名、聯(lián)機互換以及修改邏輯后,可以非常方便地回編到 Capture 線路圖中,線路圖修改后也可以非常方便地更新到 Allegro 中;用戶還可以在 Capture 與 Allegro 之間對對象的互相點選及修改。(圖 2 )

對于業(yè)界所重視的銅箔的繪制和修改功能, Allegro 提供了簡單方便的內(nèi)層分割功能,以及能夠?qū)φ撈瑑?nèi)層的檢閱。對于鋪銅也可分動態(tài)銅或是靜態(tài)銅,以作為鋪大地或是走大電流之不同應用。動態(tài)銅的參數(shù)可以分成對所有銅、單一銅或單一對象的不同程度設定,以達到銅箔對各接點可設不同接續(xù)效果或間距值等要求,來配合因設計特性而有的特殊設定。

在輸出的部分,底片輸出功能( 圖 3 )包含 274D 、 274X 、 Barco DPF 、 MDA 以及直接輸出 ODB++ 等多樣化格式數(shù)據(jù)當然還支持生產(chǎn)所需的 Pick &Place 、 NC Drill 和 Bare-Board Test 等等原始數(shù)據(jù)輸出。

Allegro 所提供的強大輸入輸出功能更是方便與其它相關軟件的溝通,例如 ADIVA 、 UGS(Fabmaster) 、 VALOR 、 Agilent ADS… 或是機構的 DXF 、 IDF……… 。為了推廣整個先進 EDA 市場 ,Allegro 提供了 OrCAD Layout 、 PADS 、 P-CAD 等接口,讓想轉(zhuǎn)換 PCB Layout 軟件的使用者,對于舊有的圖檔能順利轉(zhuǎn)換至 Allegro 中。 Allegro 有著 操作方便,接口友好,功能強大,整合性好 等諸多優(yōu)點,是一家公司投資 EDA 軟件的理想選擇!

Allegro PCB Design CIS - L將完整的設計方案所需的工具整合為一,它包含了從概念到出圖的所有工具,例如線路圖、零件庫管理、電路板設計、,自動/手動布線工具、以及其它的接口,例如機構圖甚至是其它電路板檔案的轉(zhuǎn)換接口。

不像其它的電路板設計軟件Allegro PCB Design CIS - L系列依照你的需求及技術的進步提供了可升級的方案,利用加掛的方式可增強軟件的功能,例如高速電路板的設計宣告,自動加測試點及其它的布線檢查、訊號分析需求等等,而所有的功能都是建構在經(jīng)過業(yè)界的認證Allegro PCB Design CIS - XL系列上,并且使用相同的數(shù)據(jù)平臺, 所以不管是面對現(xiàn)在或者是未來的設計挑戰(zhàn),Allegro 系列都能讓您以最適切的方案輕松應付。

快速擺放零件功能讓使用者能夠輕松的擺放重要的零件,您可選取的對象有零件名稱、零件外型、料號、訊號名,它可以自動的將零件放置到板框外,這時使用者可以很快的將重要零件區(qū)塊先行整理規(guī)劃,也可以宣告一些 “rooms” 利用他限制特定的零件需擺放至此區(qū)中,而零件宣告可以在線路圖和電路板中定義,另外也能夠定義限高區(qū)它能夠?qū)[入的零件做實時的高度檢查。

聰明的手動布線功能使使用者很容易的設計高密集板子, 利用Allegro以外型辨識、任意角度的布線引擎,您可以利用”實時推線”及”貼線布線”的走線/修線功能來輕松應對,而選項中可以控制著實時的自動整線設定使布線更能符合生產(chǎn)上的需求,而強大的手動布線功能也會依照您的設定值自動調(diào)整使達到最大的布線效益。

Allegro強大的鋪銅功能使我們很容易的來規(guī)劃內(nèi)層切割及外層鋪銅,而方便的銅箔編輯及檢查功能更使我們在處理過程達到電器上及生產(chǎn)上的種種檢查和需求。 動/靜態(tài)銅及各級設定可定義出不同接續(xù)效果或間距值等,來配合特殊的電氣特性要求。

Allegro PCB Design CIS - L能夠在線路圖與電路板之間同步化,設計者能夠自動的以同步方式更新對應,例如零件更名、邏輯閘及接點互換等等的更動,并且能很方便的將新的電路修改傳達至原電路板設計上。。

在出圖前的動作中,文字面的整理是一個非常繁復的動作,Allegro PCB Design CIS - L能夠依照使用者的設定自動的截線、 移動、旋轉(zhuǎn)、刮除文字面,使用者也能夠手動的加以調(diào)整使符合生產(chǎn)的需求,而新產(chǎn)生的文字面數(shù)據(jù)也能連動于原始的零件。

雖然有多樣且強大的功能,Allegro PCB Design CIS - L仍然是非常容易使用,首先Allegro PCB Design CIS - L擁有一個交互式的多功能教學軟件,讓使用者能很快的在幾個小時之內(nèi)了解它的操作流程,再者是Allegro PCB Design CIS - L著重于交互式的使用接口,每個輸入的字段都有方便的接口可以使用,各項設計者的需求也都有一個精靈來導引,使得指令的更容易了解 更能夠發(fā)揮以提高生產(chǎn)力。

SPECCTRA 使市面上最先進的自動及手動布線軟件,如果我們要設立的是有多重復雜的設計需求的高密度板子,SPECCTRA 使用強大的外型辨識的軟件架構,讓我們能充分的運用有限的可布線范圍, 達到最好的布線效果。擁有超過16,000 注冊的使用者SPECCTRA 是業(yè)界最被認可的自動布線軟件及技術。

現(xiàn)今的生產(chǎn)及組裝測試公司都希望能夠收到更聰明的'非gerber'式數(shù)據(jù),Allegro PCB Design CIS - L能夠提供出Valor所完全驗證過的OBD++ 數(shù)據(jù),除此之外,還可下載Valor的Valor Universal Viewer,使其它使用者能夠?qū)⑥D(zhuǎn)出的ODB++ 加載到程序中加以查看,或者利用它將底片檔轉(zhuǎn)出ODB++ ,并且可以查看由Valor's Enterprise 3000所標注的ECO's資料。]]>

Cadence設計技術公司昨日發(fā)布最新的Cadence Allegro互連設計平臺。Allegro能進一步縮短設計的時間,加強IC設計鏈,從最開始的設計到PCB的設計。

最新的Allegro技術通過在整個設計流程實現(xiàn)多人同時的PCB系統(tǒng)設計,來縮短設計周期。整個Allegro產(chǎn)品線提高了效率,并具備更加簡單易用的功能,同時使使用者能夠更快地設計更復雜的IC。

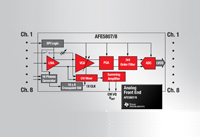

| 超聲波系統(tǒng)方框圖 | AFE5807/8 方框圖 | |

<!-- --> 超聲波系統(tǒng)方框圖 |

<!-- -->  放大 放大 |

AFE5807 和 AFE5808 超聲波 AFE 主要特性

| AFE5807 | AFE5808 | |

| 通道 | 8 | |

| 集成 | LNA+VCA+LPF+ADC+ CW 模式 | |

| 40 MSPS 時的功率 | 88 mW/通道 | 136 mW/通道 |

| 噪聲 | 1.1 nV/rtHz | 0.75 nV/rtHz |

| 14 位 ADC SNR | 74dBFS | 77dBFS |

| 封裝 | 15 mm x 9 mm 135 引腳 BGA | |

| 樣片 |  訂購 訂購 |

訂購 訂購 |

| 數(shù)據(jù)表 |  下載 下載 |

下載 下載 |

其它 AFE5807 和 AFE5808 超聲波 AFE 特性

- AFE5807 和 AFE5808 集成 8 個通道的

- 低噪聲放大器 (LNA)

- 壓控衰減器 (VCA)

- 可編程增益放大器 (PGA)

- 三階低通濾波器 (LPF)

- 具有 LVDS 輸出的 12 位和 14 位模數(shù)轉(zhuǎn)換器 (ADC)

- 集成 CW 多普勒混頻器和求和放大器提供全套 CW 波束解決方案

- AFE5807 是在 1.1nV/rtHz、40 MSPS、12 位采樣時 88mW/通道的低功率解決方案

- AFE5808 是高性能解決方案,具有 0.75nV/rtHz、140mW/通道、65 MSPS 的低噪聲優(yōu)化和 77dBFS SNR(信噪比)的 14 位模數(shù)轉(zhuǎn)換器 (ADC)

AFE5807 和 AFE5808 是 TI AFE58xx 熱門系列完全集成的模擬前端 (AFE) 中的最高性能器件,它們均用于超聲波應用。

AFE58xx 系列包括用于手持超聲波系統(tǒng)的 AFE5801 和 AFE5851 以及用于便攜式到中程超聲波系統(tǒng)的 AFE5805 和 AFE5804。所有器件均可由 TI TX810 T/R 開關在發(fā)送端添加,形成包含嵌入式處理器、模擬和電源管理解決方案的完整產(chǎn)品系列,讓制造商可以更快速地向市場推出創(chuàng)新的超聲波系統(tǒng)。

]]>選擇的生產(chǎn)方法也會影響到元件成本。例如,比較光化機(PCM)相對沖壓加工或兩種方法混合加工的成本。元件是手工安裝還是機器安裝?如果選用機器安裝,由于大多數(shù)機器采用真空吸頭吸起元件,則需要采用貼裝靶。雖然有的機器采用鉗子類型的系統(tǒng)抓起元件,但這種類型的機器并不常見。

對于機器安裝,PCB邊緣圍欄的共面性要求在0.1mm以上以保證在安裝或進入回流爐時腔體處于焊膏上。機器加工一般在返工之后,可以使用帶有指狀彈簧的蓋子,或者是焊接一個平的折疊封閉蓋子到PCB上,把暴露出來的區(qū)域重新閉合起來。這個方法可以避免最困難的工作:拆除整個屏蔽體(有可能造成PCB損壞);也可以不用為了避免最麻煩的修理工作來拆除整個單元。鑒于高容量產(chǎn)品不斷增加的復雜性和成本,以及環(huán)境指令(例如WEEE:報廢電子電氣設備指令)的實施,一個帶有穿孔的返工接觸區(qū)是一個值得認真考慮的選擇。最后,如果有很多分開的PCB區(qū)域必須與外部屏蔽,或者相互之間需要隔離,以避免串擾問題,可以采用多模穴封平圈。

元件制造方法

有很多種方法可以使用金屬制造屏蔽殼,包括光化機(PCM)、激光切割、沖壓,以及一些混合方法。選擇方法的時候主要是考慮屏蔽殼的技術需求,最終的產(chǎn)量,項目對器件價格的限制。

PCM實際上采用了和制造裸線路板的光化法同樣的流程,不同之處在于采用金屬片而不是鐵殼的絕緣體。這個過程包括制造一個平口成型產(chǎn)品。采用CAD后,要先進行蝕刻和考慮彎曲余度,再采用兩種光工具(一種用于金屬的兩面)用于標繪。兩種工具刻劃產(chǎn)品的外形的過程是一樣的。刻劃金屬一個側(cè)面的彎線,徽標,連接或者孔縫細節(jié),兩種工具采用的方法不同。金屬片要先預涂光阻膜,然后暴露在光工具的紫外光下。不需要的光阻膜會被去除,以便于蝕刻。

PCM有一些優(yōu)點,加工和工具修改花費較低,整個過程所需要的時間較短。彎線可以被很精確的蝕刻出來,例如,135,90或者45度,如圖7。整個過程沒有毛邊和金屬應力,磁和其他金屬特性不變。可以很方便的用于復雜的設計,產(chǎn)品有縫,軌道限界孔,徽標和其他細節(jié)不會增加最后的費用,這可以使設計者隨意設計他們想要的東西。

一個可以用來替換PCM的選擇是激光塑形。它用于規(guī)模生產(chǎn)小型金屬外殼時,價格并不便宜,彎線的精度也不高。但在處理很厚材料的大型屏蔽殼時很不錯,例如19英寸的齒條罩。

紐扣和螺旋壓力機可以簡單地單面塑形,但是多面同時塑形和金屬切割必須要用強力壓力機。小型壓力機可以用于手工操作一個成套沖模。大型壓力機采用機器操作,可以處理更大,多級的加工。

一個成套沖模由一對鉆孔機和底座組成,當他們被壓在一起就會在材料上打一個洞,或者把材料壓制成想要的形狀。鉆孔機和底座可以移除,鉆孔機可以在沖擊過程中臨時附在沖擊工具的末端垂直上下運動。盡管屏蔽殼的材料相對較薄,仍然需要大壓力機。因為生產(chǎn)電子產(chǎn)品的復雜結(jié)構需要指數(shù)級增長的壓力加工。這些加工需要大型機床以得到巨大的力量,這種一個可以用來替換PCM的選擇是激光塑形。它用于規(guī)模生產(chǎn)小型金屬外殼時,價格并不便宜,彎線的精度也不高。但在處理很厚材料的大型屏蔽殼時很不錯,例如19英寸的齒條罩。

紐扣和螺旋壓力機可以簡單地單面塑形,但是多面同時塑形和金屬切割必須要用強力壓力機。小型壓力機可以用于手工操作一個成套沖模。大型壓力機采用機器操作,可以處理更大,多級的加工。

一個成套沖模由一對鉆孔機和底座組成,當他們被壓在一起就會在材料上打一個洞,或者把材料壓制成想要的形狀。鉆孔機和底座可以移除,鉆孔機可以在沖擊過程中臨時附在沖擊工具的末端垂直上下運動。盡管屏蔽殼的材料相對較薄,仍然需要大壓力機。因為生產(chǎn)電子產(chǎn)品的復雜結(jié)構需要指數(shù)級增長的壓力加工。這些加工需要大型機床以得到巨大的力量,這種線穿越了PCB表面的腔體分界面。對于多層PCB板,常用的設計是將PCB射頻地放在外層,將信號走線限制在內(nèi)層

]]>logic\Auto Rename Refdes\Rename...

2.選擇"Rename"

注意:修改圖中紅色部分的參數(shù)

3.在原理圖工具Allegro HDL中:

File\Import physical...

4.點擊[OK]按鈕

( { g! }$ P$ K1 P: o; ` N! j3 b

本書以Mentor EE 2005 SP3為基礎,以具體電路為范例,詳盡講解了元器件建庫、原理圖設計、布局、布線、仿真、CAM文件輸出等PCB設計的全過程,包括原理圖輸入及集成管理環(huán)境的使用(DxDesigner及Design Capture)、中心庫的開發(fā)(Library Manager)、PCB設計工具的使用(Expedition PCB)及高速信號的仿真(Hyperlynx)。 $ q$ U6 L+ l" Y; H

+ O1 Z% P+ v4 z7 `+ O8 S

第 章 Mentor公司PCB板級系統(tǒng)設計. H2 R( s, X8 G: ]! Y

1.1 概述7 r# O. y3 R* b" s/ s: H

1.2 Mentor EE 2005部分新功能介紹0 S( R' C0 ~9 |& `. r$ o

第 章 庫管理工具(Library Manager for DxD-Expedition)$ w U/ r* H8 n- }

2.1 庫管理器(Library Manager)

2.2 庫管理工具的操作環(huán)境" E" l9 n! D1 x7 s' {2 {- W% `

2.3 新建一個中心庫4 ]& E. L5 N1 y m

2.4 中心庫設置

2.5 符號編輯器9 P6 n8 b' M: M1 N

2.6 焊盤堆編輯器8 R1 l8 @; T0 G" m# B* x

2.7 制作封裝單元(Package Cell). A, W0 |+ ~/ I! W

2.8 庫服務組件(Library Services)4 ^: H, C( D" M, h6 X9 W( S

2.9 Part DataBase(PDB)編輯器( l; U% P: }3 ~; k5 E

2.10 PCB設計模板簡介 y/ q, ^' j% {) S4 g% i ]& D

第 章 原理圖輸入工具DxDesigner

3.1 DxDesigner的操作環(huán)境

3.2 DxDesigner的基本操作) Z8 i9 X, z2 P s" i9 K

3.3 新建DxDesigner設計項目1 C% u B, ]$ b( n& g

3.4 設計配置$ e5 H: N' R5 d) X9 V

3.5 配置DxDataBook" }! K' L( o t6 S

第 章 原理圖繪制

4.1 新建原理圖

4.2 項目設置3 _0 l$ ]0 R% |' F

4.3 圖紙設置

4.4 添加元器件8 P8 ?- @+ v+ J

4.5 編輯元器件: @+ M, o& k/ d: i3 ?! s8 c

4.6 網(wǎng)絡和總線! Q& s7 `8 Q! l( V

4.7 增加或刪除圖紙; [1 u. c3 ^' M* y+ t) |. ^

4.8 原理圖的校驗

第 章 DxDesigner后處理" L" R3 \. d* S R2 h

5.1 元器件屬性4 l: m, e$ C y$ `# }) a2 e8 ]" k

5.2 Room和Cluster

5.3 約束設置

5.4 元器件清單(Part List): x d9 ^3 h$ d& A

5.5 View PCB+ }; T! x" Z% n; J6 t) d$ ~; j' c

5.6 DxDesigner原理圖與Expedition PCB的連接- k. m" C5 L j/ N/ i! {

第 章 Expedition PCB0 y1 V- j- N3 ^

6.1 Expedition PCB的操作環(huán)境

6.2 基本操作

6.3 Expedition PCB項目設置! ]; q% }1 u N7 u7 J# j1 Q% W, o

6.4 約束設置* g9 m9 b& }+ q9 Q/ B) V6 Z

6.5 創(chuàng)建PCB

第 章 PCB布局

7.1 PCB布局的一般原則

7.2 交互式布局

7.3 布局優(yōu)化

第 章 PCB布線

8.1 PCB布線的一般原則) a& s) H- ?" \) v) }

8.2 布線設置& c2 f: D' z( x2 T4 ~' b+ S1 @

8.3 建立電源/接地層

8.4 交互式布線" X; U- ^- a: A2 c

8.5 布線調(diào)整

8.6 自動布線8 s3 N2 {. g, C# L2 w+ }

8.7 沖突檢測

8.8 覆銅

第 章 高速PCB設計知識# v) _/ Y' U# e6 k3 r& ?% F

9.1 高速PCB的基本概念

9.2 PCB設計前的準備. ?( `( v. ]: H

9.3 高速PCB布線& S( z# i% C1 R. n

9.4 布線后信號完整性仿真

9.5 提高抗電磁干擾能力的措施

9.6 測試與比較

第 章 測試點/ T, z; j6 {0 A3 v. v" N

10.1 定義測試單元" k8 F: G6 J+ }' e/ b. T" K% T' W' J+ g

10.2 設置測試點參數(shù)

10.3 自動分配測試點0 K9 a, L: s; U: M3 J

10.4 交互式分配測試點# p x x8 N! N4 X

10.5 測試點報告' s, ~; C2 \1 p! F

第 章 創(chuàng)建絲印層; q4 f" ]$ c+ D

11.1 新建顯示方案" o; E% k% t! S1 p

11.2 重新標號

11.3 反標注至原理圖(Back Annotation)

11.4 生成絲印( ]: |! a9 p8 x3 \2 J! a* ^9 z" [

第 章 光繪和鉆孔數(shù)據(jù)

12.1 生成鉆孔數(shù)據(jù)

12.2 生成光繪數(shù)據(jù)

第 章 生成設計文檔

13.1 報告編寫器* d& D/ M( `4 V

13.2 相關尺寸參數(shù)及標注

第 章 庫管理工具(Library Manager for Design Capture-Expedition)

14.1 新建一個中心庫0 c9 Z- H0 N' f! a5 F1 t! l) B

14.2 中心庫設置& ], c' ~1 D* j0 ~7 b1 P& W, s

14.3 Symbol編輯器! g. l! k; J0 v! r: W

14.4 繪制Fractured Symbol

14.5 Part DataBase(PDB)編輯器

第 章 Design Capture原理圖編輯環(huán)境% ?6 u# u4 e7 g- D* A+ K

15.1 新建設計項目

15.2 項目設置4 s' e b2 P% Y

15.3 原理圖設置# a* t4 X( f0 h& w; }

第 章 Design Capture原理圖設計6 y& O% e1 x3 Z0 f8 E$ \: N1 a

16.1 放置元器件

16.2 元器件的基本操作

16.3 連接電路圖) W( A6 M* V' \. G. K

16.4 增加或刪除圖紙

16.5 添加文本標注+ g7 I$ V- D) B

第 章 Design Capture原理圖后處理

17.1 設置元器件屬性

17.2 編譯CDB網(wǎng)絡表; X6 J* p0 [# _0 ^) G

17.3 約束設置; b. ]3 | u& T6 _& i% e

17.4 封裝設計項目5 `' ?" i) b& W. W/ [3 R. y

17.5 Design Capture與Expedition PCB的接口

第 章 新建信號完整性原理圖

18.1 自由格式(Free-Form)原理圖

18.2 基于單元(Cell Based)原理圖

第 章 布線前仿真' [9 [& ?/ h6 z# ]4 l: M$ X

19.1 對網(wǎng)絡的LineSim仿真

19.2 對網(wǎng)絡的EMC分析3 }' ]1 J( l2 O. h

第 章 LineSIM的竄擾及差分信號仿真1 D% h$ \! z/ M8 m3 `* @

20.1 竄擾及差分信號的技術背景

20.2 LineSIM的竄擾分析/ k8 y- a8 K+ H+ k0 B

20.3 LineSim的差分信號仿真

第 章 Hyperlynx模型編輯器& Y" U3 g( d k& y0 I

21.1 集成電路的模型! H% R; r! R' k4 C

21.2 IBIS模型編輯器7 z" [, |9 o2 ]( M8 d \' z A7 n& q

21.3 Databook模型編輯器; e4 M' b& f/ e( Q ^

第 章 布線后仿真(BoardSim); O$ ^* L& `, W/ h& G

22.1 新建BoardSim電路板6 T0 F6 T6 z" r" Z9 y) U

22.2 快速分析整板的信號完整性和EMC問題% j$ d7 c7 y3 V

22.3 在BoardSim中運行交互式仿真

22.4 使用曼哈頓布線進行BoardSim仿真5 h8 I, V( h# b/ r0 t2 S2 }

第 章 BoardSim的竄擾及Gbit信號仿真

23.1 快速分析整板的竄擾強度4 G+ _% @2 x- L1 a7 [4 }/ c* G

23.2 交互式竄擾仿真5 _1 z8 w) e3 ^& U2 q* V! j

23.3 Gbit信號仿真! }% z+ j' M$ ]9 S1 T: q

T7 N0 `3 j' C6 F% W

+ ~9 S! T; p$ K% s

]]>

電磁兼容培訓教材

多層印制板層壓工藝技術及品質(zhì)控制

高速PCB設計指南1-8

化鎳浸金焊接黑墊之探究與改善

新編印制電路板故障排除手冊

印制電路板用化學鍍鎳金工藝探討

PCB質(zhì)量問題對三種工藝的影響.mht

Allegro如何調(diào)用AutoCAD產(chǎn)生的數(shù)據(jù).mht

Allegro轉(zhuǎn)Gerber注意事項.pdf

ALL高速PCB設計技術中文資料.pdf

BGA焊球重置工藝.pdf

CAD-CAM數(shù)據(jù)轉(zhuǎn)換的新趨勢.mht

CAM-CAD流程簡介.mht

CAM技術---資料集.chm

CAM培訓手冊.pdf

CNC鉆孔培訓教材.pdf

D-F培訓講義(一).mht

DXF 輸出重要事項.mht

FPC的最新技術動向.pdf

FPC全制程技術講解.pdf

GERBER FILE 簡介.pdf

Gerber File 數(shù)字格式的意義.mht

Gerber Format 簡介.mht

Gerber Funtion Code介紹.mht

IC封裝制程簡介.pdf

Mentor Pads2004 轉(zhuǎn) Mentor WG2004.pdf

Mentor所有 Layout 軟件翻譯名詞術語.pdf

Neopact 直接電鍍工藝的應用.mht

PCB 工藝設計規(guī)范.pdf

PCB 可測性設計.pdf

PCB 制造工藝簡述.pdf

PCB Navigator在OrCAD與PowerPCB間的應用說明.pdf

PCB板布局原則.mht

PCB板的EMC問題.pdf

PCB板返修時的兩個關鍵工藝.mht

PCB板各個層的含義.pdf

PCB板剖制的流程及技巧.mht

PCB表面最終涂層種類介紹.mht

PCB測試方法.mht

PCB廠CAM工程師應注意的事項.mht

PCB導線寬度的測量.mht

PCB的沖裁.mht

PCB的外型加工.mht

PCB電測技術分析.mht

PCB電路版圖設計的常見問題.mht

PCB對人體的危害.mht

PCB工藝流程詳解.pdf

PCB技術---資料集.chm

PCB拼板規(guī)范、標準.mht

PCB全面質(zhì)量管理.pdf

PCB設計基本工藝要求.pdf

PCB設計基礎教程.exe

PCB設計時銅箔厚度,走線寬度和電流的關系.pdf

PCB絲印網(wǎng)板制作工藝.mht

PCB外層電路的蝕刻工藝.mht

PCB網(wǎng)印中的故障與對策.mht

PCB線路板抄板方法及步驟.mht

PCB印刷線路板簡介.mht

PCB印制電路板術語詳解.pdf

PCB制造缺陷解決方法.mht

PCB專業(yè)用語.mht

PowerPCB 電路板設計規(guī)范.mht

PowerPCB 轉(zhuǎn)SCH 教程.pdf

PowerPCB設計問題集.pdf

PowerPCB轉(zhuǎn)Mentor Wg2004 過程.pdf

Protel 99SE中文教程.exe

Protel for Windows PCB 轉(zhuǎn) GERBER文件.mht

Protel PCB 轉(zhuǎn)SCH全攻略.pdf

Protel 原理圖-PCB到Cadence的數(shù)據(jù)轉(zhuǎn)換.mht

Protel99 SE Gerber File 輸出說明.mht

ProtelPCB高頻電路中布線的技巧.pdf

Protel到Allegro -CCT格式轉(zhuǎn)換.mht

Protel封裝庫至Allegro的轉(zhuǎn)化.pdf

Protel中有關PCB工藝的條目簡介.mht

PRTEL99的PCB文件生成GERBER文件流程.mht

PTH工藝指導書.mht

QFP器件手工焊接指南.pdf

RF PCB 設計.pdf

SMT & PCB.pdf

SMT技術---資料集.chm

Via孔的作用及原理.pdf

VxWorksBSP相關資料.chm

暗房操作工藝指導書.mht

暗房正負片制作在工藝區(qū)分.mht

標準和檢測技術.mht

測試探針及相關材料在測試治具中的選用.mht

常用機床的主要用途.mht

沉銅常見問題及對策.mht

籌建電路板廠規(guī)劃及實施淺述.mht

傳輸線基礎.pdf

垂直熱風整平中一些常見小問題的解決方法建議.mht

從HDI看SI.pdf

電磁兼容 試驗和測量技術 射頻電磁場輻射抗擾度試驗.pdf

電磁兼容 綜述 電磁兼容基本術語和定義的應用與解釋pdf.pdf

電磁兼容試驗和測量技術浪涌(沖擊)抗擾度.pdf

電鍍板孔邊發(fā)生圈狀水.mht

電鍍金溶液的回收工藝.mht

電鍍銅中氯離子控制.mht

電路板之微切片與切孔.mht

電容器的寄生作用與雜散電容.pdf

電子電路設計中EMC EMI的模擬仿真.mht

印制電路板設計原則和抗干擾措施.mht

鍍通孔制程(鍍通孔).pdf

鍍銅技術手冊.pdf

多層板層壓工位工藝指導書.mht

多層板的壓合制程(壓合).pdf

多層板孔金屬化工藝探討.mht

多層板孔金屬化工藝探討2.mht

多層板之內(nèi)層制作及注意事宜.pdf

多層板制作中.mht

多種不同工藝的PCB流程簡介.mht

二次銅厚度不均原因及夾膜處理.mht

氟系高頻印制板應用與基板材料簡介.mht

改善孔壁粗糙度.pdf

干膜光致抗蝕劑的結(jié)構、感光膠層的主要成分及作用.mht

干膜曝光工藝.mht

干膜使用時破孔-滲鍍問題改善辦法.mht

干膜貼膜工藝.mht

高密度、細導線、窄間距制造工藝發(fā)展動態(tài).mht

高密度多重埋孔印制板的設計與制造.pdf

高頻PCB設計中出現(xiàn)的干擾分析及對策 .pdf

高速PCB板的電源布線設計.pdf

高速PCB設計的疊層問題.pdf

高速PCB設計軟件HyperLynx使用指南.pdf

高速電路PCB板級設計技巧.pdf

高速數(shù)字電路設計.pdf

工程準備審核指導書.mht

關于多層印制板生產(chǎn)中的電鍍錫保護技術.mht

貫孔電鍍步驟說明.mht

光板測試工藝指導書.mht

光繪工藝的一般流程.mht

光繪系統(tǒng)的技術指標.mht

國外生產(chǎn)廠商型號前綴互聯(lián)網(wǎng)網(wǎng)址.pdf

焊墊表面處理(OSP,化學鎳金).pdf

烘板工藝指導書.mht

化鎳浸金量產(chǎn)之管理與解困.pdf

混合信號PCB的分區(qū)設計.mht

基材及層壓板可產(chǎn)生質(zhì)量問題的查找和解決方法.mht

基于OrCAD-PSpice9的電路優(yōu)化設計.mht

集成電路的檢測常識.mht

幾種微型電機驅(qū)動電路實驗和分析.mht

膠片收縮問題原因分析.mht

金屬化板板面起泡成因及對策探討.mht

晶振的選擇.pdf

精密磷銅陽極.mht

精品技術技巧、經(jīng)驗、文摘集錦.mht

孔金屬化板板面起泡成因及對策探討.mht

雷射成孔技術介紹與討論.mht

利用Cadence Allegro進行PCB級的信號完整性仿真.pdf

利用protel和office軟件完成電子產(chǎn)品的輔助設計.mht

利用電腦進行復雜電路板分析.mht

綠漆制程(防焊).pdf

論柔性線路板的撓曲性和剝離強度.mht

內(nèi)層板黑氧化工藝指導書.mht

內(nèi)層線路油墨水平滾涂工業(yè).mht

撓性線路板現(xiàn)狀及發(fā)展趨勢.mht

撓性印制線路板——單面、雙面.pdf

噴錫工序內(nèi)部培訓講義.mht

拼版尺寸設計簡介.pps

淺淡測試夾具制作的制作策略.mht

淺論印制板阻焊顯影.mht

淺談多層印制電路板的設計和制作.pdf

淺談數(shù)控系統(tǒng)故障診斷的一般方法.mht

去毛刺及刷板工藝指導書.mht

去膜、堿腐、晶亮工藝指導書.mht

全新的電子設計軟件protel98.mht

讓在線測試儀真正發(fā)揮作用.mht

熱風整平工藝技術.mht

熱風整平工藝露銅現(xiàn)象分析.mht

熱風整平前后處理工藝指導書.mht

日本工業(yè)標準--印制線路板通則.pdf

柔性線路板工藝資料.pdf

如 何 保 證 高 厚 徑 比.mht

如何區(qū)分菲林.mht

軟板基礎知識.mht

設計技巧.mht

射頻EDA仿真軟件介紹(包括算法,原理).mht

射頻電路PCB設計.mht

射頻電路PCB設計.pdf

射頻電路板設計技巧.pdf

生產(chǎn)工程準備作業(yè)指導書.mht

濕膜的應用技巧.mht

濕膜和滾涂技術.mht

實用印制電路板制造工藝參考資料.mht

蝕刻過程中應注意的問題.mht

蝕刻使用的相關術語.mht

數(shù)控鉆床.mht

數(shù)控鉆床-墊板.mht

數(shù)控鉆床與銑床的選用.mht

數(shù)控鉆--銑工藝.mht

印刷電路板短路處的尋找方法.pdf

雙面印制電路板制造工藝.mht

水木清華BBS精華區(qū)--數(shù)字信號處理.chm

水溶性干膜顯影工藝及常見問題的處理方法.mht

酸洗磨板工藝指導書.mht

談尼龍針刷輥使用技巧.mht

特性阻抗之詮釋與測試.pdf

提高電子系統(tǒng)設計自動化的一種方法.mht

貼片式微型保險絲小知識.mht

圖形電鍍工藝指導書.mht

圖形轉(zhuǎn)移工藝控制.mht

涂覆有機可焊保護劑OSP工藝的應用.mht

褪鉛錫工藝指導書.mht

外形加工培訓教材.pdf

微波電路及其PCB設計.pdf

微導孔與手機板.pdf

微短路,短路的發(fā)生與對策.mht

為什么PCB要使用高Tg材料.mht

顯影、蝕刻、去膜(DES)工藝指導書.mht

現(xiàn)代PCB測試的策略.mht

線路板電鍍槽的尺寸核算方法.mht

線路板基礎教材.pdf

線路板數(shù)控鉆床.mht

線路板數(shù)控鉆銑床CNC.mht

線路板細線生產(chǎn)的實際問題.mht

線路板有關標準一覽表.mht

線路板制造中溶液濃度計算方法.mht

線路電鍍(二次銅).pdf

相關文章---光圈、繪圖文件介紹.mht

芯片封裝技術知多少.pdf

芯片知識介紹.pdf

壓板掊訓教材.ppt

研磨刷輥的種類.mht

液態(tài)感光曝光、顯影工藝指導書.mht

液態(tài)感光絲印工藝指導書.mht

移動電話電磁輻射性能要求與測試方法.ppt

印刷電路板的過孔.mht

印刷電路板的設計.mht

印刷電路板圖設計的基本原則以及注意事項.mht

印刷電路板制作簡介.pdf

印制板鍍金工藝的釬焊性和鍵合功能.mht

印制板鍍銅工藝中銅鍍層針孔的原因.mht

印制板如何防止翹曲一為什么線路板要求十分平整.mht

印制板外形加工技術.mht

印制電板路設計中的工藝缺陷.mht

印制電路板材料基本分類.mht

印制電路板的可制造性--地線設計.mht

印制電路板鍍槽溶液的控制.mht

印制電路板工藝設計規(guī)范.mht

印制電路板故障排除手冊.mht

印制電路板清洗質(zhì)量檢測.mht

印制電路板水平電鍍技術.mht

印制電路板污水處理技術探討.mht

印制電路板直接電鍍研究.pdf

印制電路板制造電鍍技術簡易實用手冊.mht

印制電路板制造簡易實用手冊.mht

印制電路工藝創(chuàng)新探討.mht

印制電路工藝制程電子圖書.chm

印制電路設計中的工藝缺陷.mht

印制線路板術語中英對照.mht

影響印刷電路板(PCB)的特性阻抗因素及對策.pdf

用PROTEL99制作印刷電路版的基本流程.mht

油墨的特性和使用注意事項.mht

怎樣做一塊好的PCB板.pdf

增層法多層板與非機鉆式導孔.pdf

真空蝕刻技術.mht

整平工藝指導書.mht

制作外層線路(外層).pdf

中國印制電路工業(yè)現(xiàn)狀.mht

重氮片制作曝光檢測方法.mht

自復保險絲.pdf

阻焊油墨絲印常見問題及解決措施.mht

鉆房工藝指導書.mht

鉆孔制程(鉆孔).pdf

鉆孔質(zhì)量問題分析、快速判斷、解決方法.mht

鉆頭翻磨.mht

最新PCB及相關材料IEC標準信息 國際電工委員會.mht]]>

為此,你需要在電路板上增加退耦電容來將高速信號在電源層和地層上產(chǎn)生的噪聲降至最低。你必須知道要用多少個電容,每一個電容的容值應該是多大,并且它們放在電路板上什么位置最為合適。一方面你可能需要很多電容,而另一方面電路板上的空間是有限而寶貴的,這些細節(jié)上的考慮可能決定設計的成敗。

反復試驗的設計方法既耗時又昂貴,結(jié)果往往導致過約束的設計從而增加不必要的制造成本。使用軟件工具來仿真、優(yōu)化電路板設計和電路板資源的使用情況,對于要反復測試各種電路板配置方案的設計來說是一種更為實際的方法。本文以一個xDSM(密集副載波多路復用)電路板的設計為例說明此過程,該設計用于光纖/寬帶無線網(wǎng)絡。軟件仿真工具使用Ansoft的SIwave,SIwave基于混合全波有限元技術,可以直接從layout工具Cadence Allegro, Mentor Graphics BoardStation, Synopsys Encore和 Zuken CR-5000 Board Designer導入電路板設計。圖1是SIwave中該設計的PCB版圖。由于PCB的結(jié)構是平面的,SIwave可以有效的進行全面的分析,其分析輸出包括電路板的諧振、阻抗、選定網(wǎng)絡的S參數(shù)和電路的等效Spice模型。

|

xDSM電路板的尺寸,也就是電源層和地層的尺寸是11×7.2 英寸(28×18.3 厘米)。電源層和地層都是1.4mil厚的銅箔,中間被23.98mil厚的襯底隔開。

為了理解對電路板的設計,首先考慮xDSM電路板的裸板(未安裝器件)特性。根據(jù)電路板上高速信號的上升時間,你需要了解電路板在頻域直到2GHz范圍內(nèi)的特性。圖2所示為一個正弦信號激勵電路板諧振于0.54GHz時的電壓分布情況。同樣,電路板也會諧振于0.81GHz和0.97GHz以及更高的頻率。為了更好地理解,你也可以在這些頻率的諧振模式下仿真電源層與地層間電壓的分布情況。

圖2所示在0.54GHz的諧振模式下,電路板的中心處電源層和地層的電壓差變化為零。對于一些更高頻率的諧振模式,情況也是如此。但并非在所有的諧振模式下都是如此,例如在1.07GHz、1.64GHz和1.96 GHz的高階諧振模式下,電路板中心處的電壓差變化是不為零的。

|

找到零壓差變化點有助于我們將需要在短時間內(nèi)產(chǎn)生大量電流變化的器件放置于此。例如,如果要將一塊Xinlix的FPGA芯片放在電路板上,該芯片會在0.2納秒內(nèi)產(chǎn)生2A的輸入電流變化。如此短時間內(nèi)的大電流變化將帶來電路板的電源完整性問題,會使電路板產(chǎn)生各種模式的諧振,導致電源層和地層電壓的不均勻。然而,電路板中心處在某些諧振模式下具有零壓差變化的特性,因此將FPGA芯片放置于此可以避免電路板產(chǎn)生這些低頻的諧振模式。FPGA芯片不能激發(fā)這些低頻諧振模式,是由于從電路板的中心處將無法耦合至這些諧振模式。

圖3中的紫色曲線顯示的是當位于電路板中心處的芯片從電源平面吸入電流時引起的諧振。事實上,峰值出現(xiàn)在高階的諧振頻率1.07GHz、1.64GHz和1.96GHz上,而不是低階的諧振頻率0.54GHz、0.81GHz和0.97GHz上,這正如我們所料。

|

盡管器件的布局與放置的位置有助于減小電源完整性的問題,但它們并不能解決所有的問題。首先,你不能將所有的關鍵器件放在電路板的中心。通常情況下,器件放置的靈活性是有限的。其次,在任何給定的位置總有一些諧振模式會被激發(fā)。例如,圖3中綠色曲線表示當你將芯片放置在沿某一坐標軸偏移中心位置時,0.54GHz的諧振模式將被激發(fā)。成功的設計電路板的PDS(電源分配系統(tǒng))的關鍵在于在合適的位置增加退耦電容,以保證電源的完整性和在足夠?qū)挼念l率范圍內(nèi)保證地彈噪聲足夠小。

退耦電容

設想FPGA在0.2納秒的上升沿 吸入2A的電流,此時電源電壓會暫時降低(壓降),而地平面電壓會暫時被拉高(地彈)。其變化幅度取決于電路板的阻抗和芯片偏置管腳處的用于提供電流的退耦電容(圖4a)。

由于電流的瞬變值為2A,電壓的瞬變值由V=Z×I決定,Z是從芯片端視出的阻抗,因此,為了避免電壓的尖峰波動,在從直流到信號帶寬的頻率范圍內(nèi),Z值必須低于某一門限值。(圖4b)

|

在該設計中,為了保持電源完整性,電源—地的電壓波動必須保持在標準值3.3V的5%以內(nèi)。因此噪聲不能大于0.05×3.3V=165 mV。可以據(jù)此按照歐姆定律計算出PDS的最大阻抗165mV/2A=82.5mΩ,圖4中虛線部分即為PDS阻抗應該滿足的目標區(qū)域。

對于最低頻率,通常是1kHz或者更低的頻率——電源滿足阻抗特性的要求,電源和地層的結(jié)構通常不會破壞阻抗特性,因為它們呈現(xiàn)低電阻與電感特性。而當頻率高于1kHz時,電流通路的互感大到足以使電壓超過限定值,根據(jù):

|

對于更高的頻率,退耦電容作為電源層與地層之間的低阻抗連接是必要的。需要滿足PDS阻抗要求的信號帶寬可由下式估計:

|

在該設計中,其帶寬為1.75GHz。

為了達到這么寬的帶寬,通常需要在MHz信號區(qū)域放置很多高頻瓷片電容,在kHz信號區(qū)域放置體積較大的電解電容。這些電容矩陣與其它器件共同占用寶貴的電路板空間。在反復試驗的設計方法中,物理原型是不可缺少的,而虛擬原型技術使設計者可以在不需要物理原型的基礎上解決這個問題。

為PCB板設計PDS,例如此例中的xDSM板,使用SIwave可以在IC芯片處放置一個端口,計算電路板在適當帶寬內(nèi)的輸入阻抗。圖5中紅色曲線顯示的是電路板上無電容時的阻抗。阻抗軸與頻率軸都取對數(shù)坐標。仿真顯示了電路板本身電容的影響而忽略了經(jīng)過電源的低感應電流回路。從圖中可以看出,阻抗隨著頻率的減少而增加,但由于經(jīng)過電源的回路也有低阻抗,因此這種關系并不是嚴格的。

|

根據(jù)Z=1/(j·C),紅色曲線中的直線部分表明電路板本身的電容為74nF。為了使阻抗在1MHz處低于目標阻抗82.5mΩ,電容值至少應為2μF——幾乎是電路板本身電容的30倍。為此首先需要增加22個0.1μF的電容矩陣。圖中深藍色曲線是經(jīng)過重新設計后的阻抗特性。在大多數(shù)的頻率范圍內(nèi),設計滿足了阻抗特性的要求。但在帶寬的高端,電容的ESL(等效串聯(lián)電感)、ESR(等效串聯(lián)電阻)以及由電容間距帶來的附加電感使阻抗曲線沒有達到阻抗特性要求。

由于更小的電容具有更小的ESL和ESR值,因此增加旁路有助于提高其高頻特性。圖5中的淺藍色曲線是又增加10nF電容矩陣后的阻抗曲線。綠色曲線表示再次增加1nF電容矩陣后的結(jié)果。每一級別電容矩陣的增加都提高了阻抗特性,但結(jié)果仍然剛剛滿足阻抗特性的要求。

在設計的這個階段,設計者可以增加電磁仿真與電路仿真一起來完成設計。這種方法使設計者可以精確地為低端的阻抗建模,包括電源的負載效應。它也可以直接仿真電源管腳上的噪聲從而直接驗證電源層噪聲,避免對電源層阻抗的過多分析導致的不必要的設計開銷。

首先應在選定的位置添加輸入和輸出端口。上文已經(jīng)在一個IC芯片處添加了端口,接著應該在電源輸入端添加一個端口,同時在其它兩塊芯片的安裝位置添加兩個端口。然后在SIwave中你可以進行寬頻掃描,在整個帶寬內(nèi)獲得4×4的S參數(shù)散射矩陣。接下來可以使用Full-Wave Spice產(chǎn)生與Spice兼容的電路文件以便在電路仿真環(huán)境中進一步分析。

在產(chǎn)生的電路文件中,PCB板在電路的中心位置。電路文件還包括FPGA的模型——伴有一個電流探針和一個差分電壓探針的電流源。Full-wave Spice創(chuàng)建的Spice電路還包括上文提到的三個電容矩陣。如果在IC處再增加第四個電容矩陣將進一步減小高端阻抗。電路還包括一個直流電源,電源伴有少量容值從1nF到100μF的退耦電容。另外還包括其它兩個IC芯片的模型,周圍伴有少量100nF的電容矩陣。

|

圖6顯示了FPGA的電源電壓的噪聲仿真結(jié)果。紅色曲線代表芯片輸入電流的突變——在0.2納秒內(nèi)電流由0A變化到2A。藍色曲線表示沒有添加最后一組電容矩陣時IC芯片的電壓曲線。與3.3V相比,電壓的波動已經(jīng)很小了,但還是超過了5%的規(guī)范要求。綠色曲線表示添加了第四組電容矩陣后電壓的波動曲線,最終的設計滿足了電源噪聲小于165mV的規(guī)范要求。

可以用同樣的方法分析電路板上其它的芯片,保證他們不受電源壓降和地彈的影響。在本例中另外兩芯片分別吸收100mA和50mA電流,相對來說,它們對噪

為了應對以上挑戰(zhàn),業(yè)界引入了SiP的概念,即把多個不同的元件集成在一個基底(substrate)上,而不是一個裸片(die)上。SiP不僅開發(fā)周期短,而且NRE成本低,SiP現(xiàn)被廣泛應用于無線、網(wǎng)絡和消費電子應用,諸如手機、藍牙模塊、WLAN模塊和網(wǎng)絡包交換。Semico市場研究公司的報告也顯示,到2007年SiP合同制造商的收入將達到747.9百萬美元。SiP很可能會變成一個主流的技術趨勢。為了滿足這一日益增長的設計需求,Cadence設計系統(tǒng)有限公司最近推出了業(yè)界第一套完整的能夠推動SiP IC設計主流化的EDA產(chǎn)品,它們提供了將許多IC設計和封裝技術整合在一起的能力,從而使得更多的IC設計工程師可以開發(fā)出成本、尺寸和性能都更為優(yōu)化的高集成度產(chǎn)品。

Cadence解決方案通過提供一套全自動的、整合的、可靠的和可重復的設計流程,解決了目前SiP設計中依賴專家工程技能的方法所固有的局限性,從而可滿足市場對無線和消費電子產(chǎn)品不斷增長的需求。這些新產(chǎn)品包括了RF SiP Methodology Kit,它由兩款新的RF SiP產(chǎn)品(SiP RF Architect和SiP RF Layout)和三款新的數(shù)字SiP產(chǎn)品(SiP Digital Architect、SiP Digital SI和SiP Digital Layout)構成。RF SiP Methodology Kit提供了一個基于仿真的IC/封裝協(xié)同流程,它解決了一些關鍵的SiP設計挑戰(zhàn),如缺少整合的工具和方法來實現(xiàn)系統(tǒng)、IC、封裝和電路板設計的整合,以及無法仿真、驗證和分析完整的SiP設計。

| Cadence最近推出的SiP設計套件提供了將許多IC設計和封裝技術整合在一起的能力。 |

| 作者:Jake Chen; 執(zhí)行主編; 《電子系統(tǒng)設計》 |

RF SiP Methodology Kit目前支持大多數(shù)主要晶圓代工廠的大多數(shù)主流工藝技術,支持從原理圖到GDSII的完整流程(包括用于全系統(tǒng)仿真的參數(shù)背注),支持SystemC和SystemVerilog,也可以利用Mathworks Mathlab的系統(tǒng)級鏈接接口進行ESL驗證。

RF SiP Methodology Kit提供了一種快速集成多個裸片的設計方法,從而提供了一種完整SoC實現(xiàn)的替代方法。Cadence RF Design Methodology Kit解決了將功放、PLL、VCO和濾波器放到單個SoC上的集成挑戰(zhàn)。

Cadence SiP解決方案可以與Cadence 主要的設計平臺無縫整合,如可以與Encounter整合實現(xiàn)裸片抽象級協(xié)同設計,與Virtuoso整合實現(xiàn)RF模塊設計,與Allegro整合實現(xiàn)封裝與電路板的協(xié)同設計以提供尺寸、成本和性能都更為優(yōu)化的終端產(chǎn)品。下一步Cadence將開發(fā)可把整個無線系統(tǒng)集成在一個SiP或SoC上的套件產(chǎn)品。

RF SiP Kit包括新的Cadence SiP RF產(chǎn)品和設計方法,它們可自動化和加速用于無線通信應用的RF SiP產(chǎn)品的整個設計流程。它也提供了基于802.11 b/g無線局域網(wǎng)設計的經(jīng)過客戶驗證的SiP實現(xiàn)方法,這使得客戶能夠以很低的風險快速和順利地采用SiP設計技術。這個套件與Cadence之前發(fā)布的Cadence RF Design Methodology Kit一起拓展了Cadence在無線RF設計領域的產(chǎn)品線。目前Freescale和Jazz半導體公司已經(jīng)在采用該套件開發(fā)RF產(chǎn)品。

]]>商業(yè)挑戰(zhàn)面前,半導體產(chǎn)業(yè)的技術挑戰(zhàn)也愈加棘手。隨著集成電路工藝在從微米時代步入納米時代,如今要經(jīng)歷從90nm、65nm、45nm、32nm的工藝提升,同時物理現(xiàn)象也發(fā)生變化,不同的工藝帶來不同的設計挑戰(zhàn)。現(xiàn)在,最重要的挑戰(zhàn)是低功耗。漏電流是65nm面對的第一大問題,物理現(xiàn)象改變了,設計方法和工具也要改變。此外,良率、可靠性、高集成度都是技術方面的挑戰(zhàn)。

從概念到產(chǎn)品推向市場,EDA服務于產(chǎn)業(yè)鏈整合

半導體產(chǎn)業(yè)發(fā)展到今天,EDA作為IC設計不可或缺的支撐工具,要在“最短時間、開發(fā)出最低成本、最復雜的產(chǎn)品”,僅僅提供“點”工具是不夠的。

因此,居龍指出:“當今,整個設計鏈(包括設計、制造、封裝)分工越來越細,F(xiàn)abless遠遠多于IDM(集成器件制造商),單個公司無法面對所有的工作,公司成功與否取決于產(chǎn)業(yè)鏈整合是否高效。從概念到市場,EDA工具要服務于產(chǎn)業(yè)鏈的整合,包括從系統(tǒng)級設計、物理實現(xiàn)、封裝設計、加工制造、PCB設計整個過程,都需要EDA工具的輔助支持。”

從概念到產(chǎn)品推向市場,整個電子設計分為幾塊:IC設計->封裝設計->IC制造->PCB設計。“整個設計周期大概需要半年到一年時間,一個產(chǎn)品才可以推向市場。在IC制造、PCB設計環(huán)節(jié)等環(huán)節(jié)都存在一些技術設計挑戰(zhàn),會影響到產(chǎn)品上市時間、良率。”該公司資深設計服務專家賴志廣講解了EDA的角色,“在整個設計流程中EDA都守候在一旁,提供一個輔助平臺,對所有產(chǎn)品設計流程中提供強有力的幫助。”

Cadence的技術平臺分為5個不同的產(chǎn)品線,全面的設計工具可以提供從概念到產(chǎn)品實現(xiàn)最完整的解決方案。包括針對大規(guī)模、復雜、高性能的數(shù)字IC設計平臺Encounter;用于模擬、混合信號、RF集成電路設計的全定制設計平臺Virtuoso;支持最快、最有效大規(guī)模復雜芯片驗證的功能驗證平臺Incisive;面向目標、按時完成系統(tǒng)協(xié)同設計的系統(tǒng)互聯(lián)設計平臺Allegro,以及在生產(chǎn)加工前進行可信賴加工驗證的可制造性設計技術。

垂直解決方案(或稱“錦囊”)是Cadence為幫助IC設計公司迅速建立設計架構,并獲得更短、可預測性更高的設計周期而推出的,獨具特色的整套解決方案。“錦囊”通過與一個打包在平臺流程中經(jīng)過驗證的方法學、授權標準IP相結(jié)合,用于解決特定的應用設計問題。當前,Cadence的“錦囊”重點在無線領域,以及有線網(wǎng)絡、個人娛樂領域,已有5個方案(包括RF SiP Methodology Kit、Functional Verification Kit for ARM、AMS Methodology Kit、Optimization Methodology Kit for ARM Processors、RF Design Methodology Kit)。

“Cadence有最完整的解決方案,能夠為客戶提供全面的增值,這是我們的優(yōu)勢。”居龍也進一步解釋了小公司難成氣候,“今后幾年大公司就變成大者恒大,小公司生存空間非常小,頂多做出一個不錯的技術賣給大公司,不可能再會上市。”

系統(tǒng)功能驗證、可制造性設計是未來成長空間

傳統(tǒng)EDA市場主要集中在RTL和GDS。如今,在EDA市場增長遭遇瓶頸的大環(huán)境下,業(yè)界都在探尋EDA新的成長空間。

居龍談到Cadence要把握兩個新的成長空間,這也是Cadence看到的客戶需求。

一方面,芯片和系統(tǒng)的結(jié)合越來越緊密,要把系統(tǒng)所有功能放到芯片上去,將面臨系統(tǒng)功能驗證的挑戰(zhàn),因而Cadence現(xiàn)在一個新的產(chǎn)品方向是提供系統(tǒng)功能驗證的解決方案,使產(chǎn)品從規(guī)格設計到實現(xiàn)能很快實現(xiàn)。

另一方面是制造,IC設計完成后,但是否以很好的成本生產(chǎn)出來,以及跟fountry的結(jié)合是否夠密切,可制造性設計(DFM)也是未來發(fā)展方向。Cadence和PDF Solutions已就DFM架構藍圖開發(fā)開始合作。

在中國市場,Cadence也正在與信息產(chǎn)業(yè)部就合作事宜進行積極磋商。談到Cadence與中國政府在IP合作上的考慮,居龍稱:“Cadence希望與政府合作不是要賣IP,而是通過與政府政策帶動整個產(chǎn)業(yè)。我們的想法是:自己不賣IP,而是希望把國外IP帶進來,國外IP公司要進入中國,一方面他們擔心自己IP被侵權,另一方面怎樣幫助他們把IP真正利用起來,像MIPS、ARM吸引很多支持,能不能及如何進行驗證、集成。”他強調(diào),IP不是獨立的,只有設計出真正的產(chǎn)品它才有價值,而像Intel真正有價值的IP也是不賣的。

]]>

| |||||||

|

《電子技術應用》2000年12期的精華文章.chm

2000-2001年我國電子信息產(chǎn)品進出口形勢回顧 Allegro轉(zhuǎn)Gerber注意事項.pdf

ALL高速PCB設計技術中文資料.pdf

BGA焊球重置工藝.pdf

CAD-CAM數(shù)據(jù)轉(zhuǎn)換的新趨勢.mht

CAM-CAD流程簡介.mht

CAM技術---資料集.chm

CAM培訓手冊.pdf

CNC鉆孔培訓教材.pdf

撓性印制線路板——單面、雙面.pdf

DXF 輸出重要事項.mht

FPC的最新技術動向.pdf

FPC全制程技術講解.pdf

GERBER FILE 簡介.pdf

Gerber File 數(shù)字格式的意義.mht

Gerber Format 簡介.mht

Gerber Funtion Code.mht

IC封裝制程簡介.pdf

Mentor Pads2004 轉(zhuǎn) Mentor WG2004.pdf

Mentor所有 Layout 軟件翻譯名詞術語.pdf

PCB 工藝設計規(guī)范.pdf

PCB 可測性設計.pdf

PCB 制造工藝簡述.pdf

印制電路板設計原則和抗干擾措施.mht

PCB板的EMC問題.pdf

PCB板返修時的兩個關鍵工藝.mht

PCB板各個層的含義.pdf

PCB表面最終涂層種類介紹.mht

PCB測試方法.mht

PCB電路版圖設計的常見問題.mht

PCB工藝流程詳解.pdf

PCB技術---資料集.chm

PCB全面質(zhì)量管理.pdf

PCB設計基本工藝要求.pdf

PCB設計基礎教程.exe 1

PCB設計時銅箔厚度,走線寬度和電流的關 PCB外層電路的蝕刻工藝.mht

PCB印制電路板術語詳解.pdf

PCB制造缺陷解決方法.mht

PowerPCB 轉(zhuǎn)SCH 教程.pdf

PowerPCB設計問題集.pdf

PowerPCB轉(zhuǎn)Mentor Wg2004 過程.pdf

Protel 99SE中文教程.exe

Protel for Windows PCB 轉(zhuǎn) GERBER文件.mht

Protel PCB 轉(zhuǎn)SCH全攻略.pdf

Protel99 SE Gerber File 輸出說明.mht

ProtelPCB高頻電路中布線的技巧.pdf

Protel封裝庫至Allegro的轉(zhuǎn)化.pdf

Protel中有關PCB工藝的條目簡介.mht

PRTEL99的PCB文件生成GERBER文件流程.mht

QFP器件手工焊接指南.pdf

RF PCB 設計.pdf

SMT & PCB.pdf

SMT技術---資料集.chm

Via孔的作用及原理.pdf

VxWorksBSP相關資料.chm

標準和檢測技術.mht

籌建電路板廠規(guī)劃及實施淺述.mht

從HDI看SI.pdf

電磁兼容 試驗和測量技術 射頻電磁場輻射抗 電磁兼容 綜述 電磁兼容基本術語和定義的應 電磁兼容試驗和測量技術浪涌(沖擊)抗擾 電容器的寄生作用與雜散電容.pdf

電子電路設計中EMC EMI的模擬仿真.mht

印刷電路板短路處的尋找方法.pdf

鍍通孔制程(鍍通孔).pdf

鍍銅技術手冊.pdf

多層板的壓合制程(壓合).pdf

多層板之內(nèi)層制作及注意事宜.pdf

改善孔壁粗糙度.pdf

高密度、細導線、窄間距制造工藝發(fā)展動態(tài).mht

高密度多重埋孔印制板的設計與制造.pdf

高頻PCB設計中出現(xiàn)的干擾分析及對策 .pdf

高速PCB板的電源布線設計.pdf

高速PCB設計軟件HyperLynx使用指南.pdf

高速電路PCB板級設計技巧.pdf

高速數(shù)字電路設計.pdf

貫孔電鍍步驟說明.mht

光繪工藝的一般流程.mht

光繪系統(tǒng)的技術指標.mht

國外生產(chǎn)廠商型號前綴互聯(lián)網(wǎng)網(wǎng)址.pdf

焊墊表面處理(OSP,化學鎳金).pdf

線路板細線生產(chǎn)的實際問題.mht

化鎳浸金量產(chǎn)之管理與解困.pdf

混合信號PCB的分區(qū)設計.mht

幾種微型電機驅(qū)動電路實驗和分析.mht

晶振的選擇.pdf

精品技術技巧、經(jīng)驗、文摘集錦.mht

孔金屬化板板面起泡成因及對策探討.mht

雷射成孔技術介紹與討論.mht

利用Cadence Allegro進行PCB級的信號完整性 利用protel和office軟件完成電子產(chǎn)品的輔助 利用電腦進行復雜電路板分析.mht 綠漆制程(防焊).pdf

高速PCB設計的疊層問題.pdf

拼版尺寸設計簡介.pps

淺談多層印制電路板的設計和制作.pdf

全新的電子設計軟件protel98.mht

讓在線測試儀真正發(fā)揮作用.mht

日本工業(yè)標準--印制線路板通則.pdf

柔性線路板工藝資料.pdf 設計技巧.mht

射頻電路PCB設計.pdf

射頻電路板設計技巧.pdf

實用印制電路板制造工藝參考資料.mht

蝕刻過程中應注意的問題.mht

數(shù)控鉆--銑工藝.mht

印制板如何防止翹曲一為什么線路板要求十分 雙面印制電路板制造工藝.mht

]]>